В одном из предыдущих постов, а именно — посте Учимся программировать под FPGA на SystemVerilog , мы познакомились с основами разработки под FPGA, а также платой Arty Artix-7 и средой разработки Vivado от компании Xilinx. Помимо прочего, было сказано, что все ПО в мире FPGA является закрытым и совместимым только с железом конкретного производителя (то есть, полный вендор лок). Так вот, оказывается, что это не совсем правда. Открытое ПО для разработки под FPGA все-таки существует, и сегодня мы научимся с ним работать.

Теоретическая часть

Есть проект IceStorm , который ставит перед собой целью реверс-инжиниринг и документирование внутреннего устройства FPGA серии iCE40 от компании Lattice, а также предоставление открытого ПО для разработки под эти FPGA. С этим проектом тесно связаны утилиты Yosys и Arachne-pnr , предназначенные, собственно, для компиляции кода на Verilog или SystemVerilog. Первая утилита выполняет синтез, а вторая — имплементацию, а точнее, один из шагов имплементации под названием place and route . Наконец, конфигурирование FGPA выполняется с помощью утилит icepack и iceprog, являющихся частью пакета IceStorm.

Fun fact! Существуют экспериментальные графические среды разработки на базе IceStorm под названием IceStudio и Apio IDE . Кроме того, поддержка iCE40 заявлена в вовсе не экспериментальной PlatformIO . В рамках данной заметки, впрочем, эти среды разработки не рассматриваются.

Fun fact! Официальная среда разработки под FPGA серии iCE40 называется iCECube2 . У нее есть версия под Linux и, насколько я смог разобраться, Lattice не берет денег за ее использование. Во всяком случае, пока что.

Помимо прочего, серия iCE40 интересна тем, что существуют весьма недорогие девборды на основе этих FPGA. Так, официальная стоимость Lattice iCEstick на базе чипа ICE40HX1K составляет всего лишь 22$. Плату можно купить на AliExpress или eBay (ищите по запросу «ICE40HX1K»), хотя и с некоторой наценкой. Наконец, существуют и альтернативные платы, также весьма недорогие. Небольшая цена делает эти платы крайне привлекательными для тех, кто хочет поиграться с FPGA чисто чтобы понять, насколько это интересное или не интересное занятие.

Из минусов тут стоит отметить небольшое количество логических ячеек у FPGA серии iCE40, что ограничивает их области применения. Согласно даташиту [PDF] , чип ICE40HX1K имеет 1280 логических ячеек против 33208 у Artix-7 XC7A35T, рассмотренной в предыдущей статье. Самый мощный чип из серии, ICE40HX8K, имеет лишь 7680 логических ячеек.

Дополнение: 24 ноября 2017 стартовали продажи платы TinyFPGA B2 на базе чипа ICE40LP8K, имеющего 7680 логических ячеек. Цена платы составляет 34$. Есть плата расширений . Из плат на базе iCE40 еще существует, например, IceZUM Alhambra . Правда, плата использует чип ICE40HX1K и стоит 75$. То есть, TinyFPGA B2 и дешевле и мощнее. Также есть плата BlackIce II на базе ICE40HX4K. Эта плата помимо самого FPGA также имеет 32-х битный микроконтроллер STM32 . Еще заслуживает внимания плата Nandland Go Board . Плата основана на простеньком ICE40HX1K, зато работает на частоте 25 МГц и имеет встроенный VGA-разъем, что делает ее весьма удобной для экспериментов с видео. Цена платы составляет 65$ + 12$ доставка. Наконец, компания Olimex выпускает платы iCE40HX1K-EVB (~33$), iCE40HX8K-EVB (~62$), а также многочисленные платы расширений к ним.

Спрашивается, а неужели это так важно, является ли ПО для разработки открытым или закрытым? На самом деле, разумеется, это не так уж и важно. Что действительно важно, по крайней мере, лично для меня, это удобство ПО. И если говорить конкретно про Vivado, то пользоваться им, конечно, можно, но особо удобным я его не назвать не могу.

Интерфейс у Vivado жуткий, особенно если весь остальной код вы привыкли писать в Vim или Sublime Text . Кроме того, интерфейс этот заметно тормозит. Просто взять и поставить Vivado из пакетов нельзя, нужно проходить регистрацию с идиотскими вопросами и качать огромный архив, который потом отожрет у вас на диске 16 Гб непонятно подо что. Проекты, создаваемые Vivado, можно использовать с системами контроля версий примерно никак, ибо не ясно, какие файлы нужны среде разработки, а какие можно смело добавить в .gitignore. Наконец, насколько я смог разобраться, после года использования Vivado превращается в тыкву и начинает хотеть больше денег.

В связи с этим, до тех пор, пока мне хватает возможностей iCEstick, а мне их пока что хватает, я предпочел бы держаться подальше от тяжелых и неудобных сред разработки как компании Xilinx, так и Altera.

Практическая часть

Нам понадобятся следующие пакеты:

Названия приведены для Arch Linux . В других дистрибутивах Linux пакеты могут называться немного иначе, или вовсе отсутствовать. В последнем случае потребуется скачать их с GitHub и собрать самостоятельно.

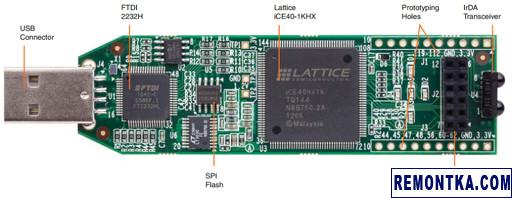

Плата iCEstick выглядит приблизительно так:

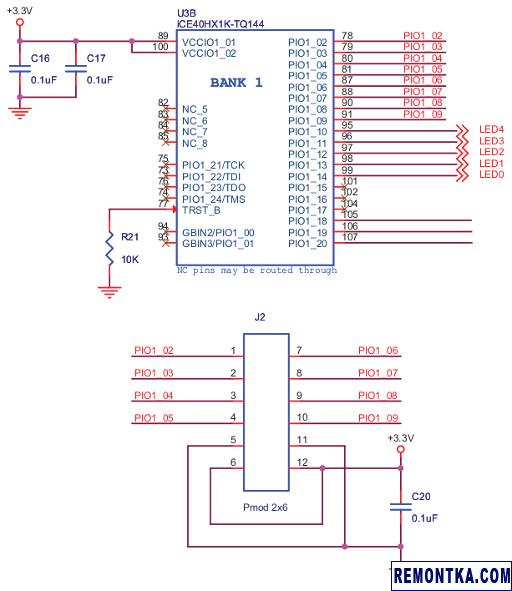

Для нас особый интерес представляют пины в правой ее части, поскольку именно через них мы будем считывать кнопки, мигать светодиодами, и вот это вот все. Номера пинов в верхней части (J1) и нижней части (J3) подписаны, поэтому с ними особых проблем не возникает. Для J1 слева на право пины идут в порядке 119, 118, …, 112, GND, 3.3V, а для J3 — в порядке 44, 45, 47, 48, 56, 60, 61, 62, GND, 3.3V. Пины, расположенные посередине (J2), к сожалению, на шелкографии не подписаны. Однако их номера не сложно узнать из схемы платы, приведенной в документе под названием iCEstick User Manual [PDF] :

Кроме того, из этой схемы мы теперь знаем, к каким пинам подсоединены пять светодиодов, расположенных на плате.

Для своих страшных экспериментов я примотал макетную плату прямо к iCEstick при помощи двух нейлоновых стяжек, а уже на макетке расположил кнопку и светодиоды. Вот, что получилось в итоге:

За основу проекта был взят пример под названием rot из исходников Arachne-pnr. В файле rot.pcf мы говорим, на каких пинах нужно искать кнопку, светодиоды и тики от часов:

set_io D2 118

set_io D3 117

set_io D4 116

set_io D5 95

set_io sw 44

set_io clk 21

Код на SystemVerilog содержится в файле rot.sv:

output D1 , output D2 , output D3 , output D4 ,

output D5 ) ;

reg ready = 0 ;

reg [ 23 : 0 ] divider ;

reg [ 3 : 0 ] rot ;

reg [ 1 : 0 ] blink ;

reg tmp ;

always @ ( posedge clk )

begin

if ( ready )

begin

if ( divider == 6000000 )

begin

divider <= 0 ;

rot <= { rot [ 2 : 0 ] , rot [ 3 ] } ;

blink <= { blink [ 0 ] , blink [ 1 ] } ;

end

else

divider <= divider + 1 ;

end

else

begin

ready <= 1 ;

rot <= 4’b0001 ;

blink <= 2’b01 ;

divider <= 0 ;

end

if ( sw == 0 )

tmp <= 0 ;

else

tmp <= blink [ 0 ] ;

end

assign D1 = rot [ 0 ] ;

assign D2 = rot [ 1 ] ;

assign D3 = rot [ 2 ] ;

assign D4 = rot [ 3 ] ;

assign D5 = tmp ;

endmodule

Как несложно понять по коду, светодиоды на макетке загораются и гаснут один за другим. Кроме того, мигает зеленый светодиод на самом iCEstick, но только в том случае, если нажата и удерживается кнопка на макетной плате.

Наконец, файл make.sh предназначен для сборки проекта и конфигурирования FPGA:

set -e

yosys -p «synth_ice40 -blif rot.blif» rot.sv

arachne-pnr -d 1k -P tq144 -p rot.pcf rot.blif -o rot.asc

icepack rot.asc rot.bin

iceprog rot.bin

Интересно, что yosys поддерживает команду show , предназначенную для визуализации полученной конфигурации на различных уровнях абстракции. Найти подробности по этой теме и полюбоваться скриншотами можно здесь . Следует также отметить, что в пакет IceStorm входит утилита icetime, умеющая искать критические пути:

Впрочем, используя часы с частотой менее 100 МГц, вам вряд ли придется сильно беспокоиться о критических путях. Рассматриваемая нами плата Lattice iCEstick, к примеру, работает на частоте всего лишь 12 МГц.

Заметьте, что если вы используете чип, отличный от ICE40HX1K, ключи утилит arachne-pnr и icetime могут немного отличаться. Подробности можно найти в табличке на сайте IceStorm .

А как быть с симуляцией?

Для Verilog и SystemVerilog есть несколько открытых симуляторов . Мне лично понравился Icarus Verilog (он же iverilog), поэтому я расскажу о нем. Для примера рассмотрим симуляцию кода из предыдущего поста, посвященного плате Arty Artix-7, а затем сравним результаты, полученные при помощи Vivado и Icarus Verilog.

Файл hello.sv остается без изменений:

module hello (

input logic CLK100MHZ ,

input logic [ 3 : 0 ] sw ,

output logic [ 3 : 0 ] led

) ;

// iverilog doesn’t support `always_ff`

always @ ( posedge CLK100MHZ )

begin

if ( sw [ 0 ] == 0 )

begin

led <= 4’b0001 ;

end

else

begin

led <= 4’b0000 ;

end

end

endmodule

А вот файл hello_sim.sv придется немного подправить:

module hello_sim ( ) ;

logic clck_t ;

logic [ 3 : 0 ] sw_t ;

logic [ 3 : 0 ] led_t ;

hello hello_t ( clck_t , sw_t , led_t ) ;

initial begin

clck_t <= 0 ;

sw_t <= 4’b0000 ; # 1 ; clck_t <= 1 ; # 1 ; clck_t <= 0 ; # 1 ;

$display ( «%b» , led_t ) ;

sw_t <= 4’b0001 ; # 1 ; clck_t <= 1 ; # 1 ; clck_t <= 0 ; # 1 ;

$display ( «%b» , led_t ) ;

end

initial begin

$dumpfile ( «hello.vcd» ) ;

$dumpvars ;

end

endmodule

Симуляция прогоняется так:

. / sim

Вывод программы sim будет следующим:

0001

0000

Здесь 0001 и 0000 — это значения sw_t, выведенные при помощи $display .

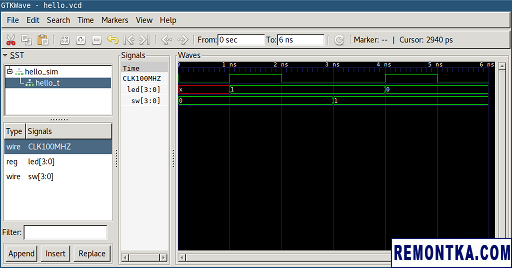

Сгенерированный файл hello.vcd можно просмотреть в GTKWave:

В итоге увидим нечто вроде:

Как видите, результат ничем не хуже полученного при помощи Vivado. Стоит однако отметить, что на момент написания этих строк iverilog не имел поддержки SystemVerilog Assertions (SVA) , которая есть у Vivado.

Заключение

Как мы только что убедились, СПО для разработки под FPGA не только существует, но и отлично работает. Главное же ограничение этого СПО заключается в небольшом списке поддерживаемых FPGA. Не знаю, как вы, а мне бы искренне хотелось, чтобы со временем перечень FPGA, поддерживаемых IceStorm, Yosys и Arachne-pnr, был расширен.

Если у вас есть сомнения по поводу того, насколько все описанное в данном посте применимо для более серьезных проектов, чем мигание четырьмя светодиодами, рекомендую посмотреть видео A Free and Open Source Verilog-to-Bitstream Flow for iCE40 FPGAs (спойлер — вполне применимо). Если вам хочется узнать больше о внутреннем устройстве FPGA серии iCE40 или почерпнуть знания о возможности создавать множественные конфигурации для этих чипов, рекомендую видео A low-level view at the Lattice iCE40 HX1K/HX8K FPGA .

Также вас могут заинтересовать:

- Open FPGA Verilog Tutorial за авторством Juan Gonzalez-Gomez ;

- Туториалы на сайте nandland.com за авторством Russell Merrick ;

- Вопросы на StackOverflow с тэгом «yosys» ;

- Тематический сабредит ;

- ICE40 floorplan позволяет посмотреть, как физически выглядит ваша конфигурация FPGA ;

Исходники к посту, как обычно, вы найдете на GitHub .

Дополнение: См также заметки Превращаем плату iCEstick в логический анализатор , Как я делал электронные часы на базе FPGA , Генерация синусоидального сигнала, а следовательно и звука, на FPGA и Учим iCEstick передавать видео-сигнал по VGA .