В продолжение темы о сдвиге фазы ВЧ-сигналов хотелось бы рассмотреть еще одну схему. Схема на этот раз основана на активном компоненте. А именно, сдвоенном D-триггере 74HC74. Давайте же разберемся в плюсах и минусах такого решения.

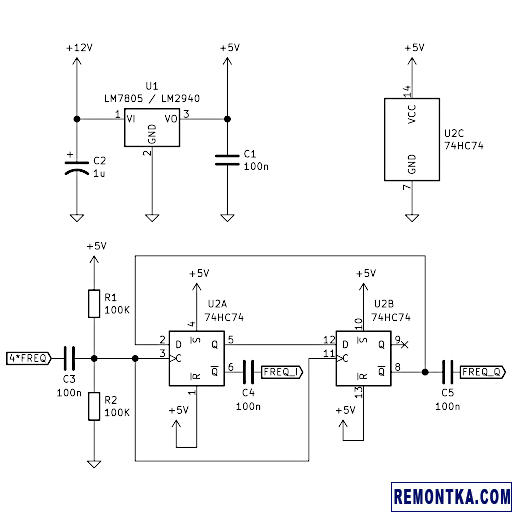

Есть несколько вариантов схемы, но идея везде одинаковая:

Для понимания схемы вспомним, как работает D-триггер . Когда на вход C приходит передний фронт тактового сигнала, триггер смотрит на вход D и подает соответствующее напряжение, высокое или низкое, на выход Q. В остальное время состояние триггера не изменяется. Выход !Q всегда имеет значение, обратное Q. Дополнительные входы !R и !S позволяют установить начальное состояние, игнорируя тактовый сигнал. В данной схеме они не используются, но подробности можно найти в даташите [PDF] .

Произвольным образом выберем начальное состояние системы и подумаем, как оно будет меняться со временем:

— 0 1 0

↑ 0 1 1

↑ 1 0 1

↑ 1 0 0

↑ 0 1 0

↑ 0 1 1

↑ 1 0 1

…

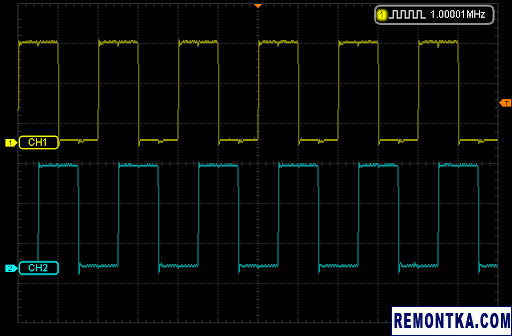

Через каждые четыре такта состояние системы повторяется. Можно также заметить, что выходы !Q6 и !Q8 меняются одинаковым образом. Два такта они имеют низкое напряжение, а затем два такта — высокое. Только выход !Q6 обновляется на один такт раньше по сравнению с выходом !Q8. Другими словами, мы имеем два меандра, сдвинутых относительно друг друга на 90°.

Осталось только убедиться, что это действительно работает:

Частота сигнала на входе должна быть в четыре раза больше желаемой частоты сигналов на выходе. Входной сигнал не обязан быть меандром, все прекрасно работает и с синусом. Требуемый уровень входного сигнала — 12 dBm (2.5 Vpp). Измеренный уровень основного тона выходных сигналов в нагрузку 50 Ом составил 13 dBm.

Схема работает корректно при частоте входного сигнала ≤ 59 МГц, что позволяет получить ≤ 14.750 МГц на выходе. Впрочем, тут все зависит как от производителя 74HC74, так и от конкретного экземпляра чипа. Texas Instruments в своем даташите [PDF] заявляет F max не менее 29 МГц, притом типичное значение не сообщается. NXP при температуре от -40 до +85 °C обещает [PDF] F max не менее 28 МГц, и типичное значение от 69 МГц до 82 МГц, в зависимости от напряжения питания, 4.5 В и 6 В соответственно. Аналогичный чип 74ACT74 от Texas Instruments имеет [PDF] F max не менее 125 МГц и типичное значение — 210 МГц. Я использовал 74HC74 производства NXP.

Главным преимуществом схемы является тот факт, что она одинаково хорошо работает в широком интервале частот. К недостаткам следует отнести то, что на входе требуется сигнал высокой частоты, и что максимальная частота выходного сигнала ограничена.

Дополнение: Схема нашла применение в трансивере AYN/DC . В продолжение темы см статьи Генерация сигналов с фазовым сдвигом при помощи Si5351 , Квадратурный демодулятор на основе 74HC4053 и Квадратурный сэмплирующий детектор по схеме Тейло .