История создания очень популярной микросхемы и описание ее внутреннего устройства

Одной из легенд электроники является микросхема интегрального таймера NE555 . Разработана она была в далеком 1972 году. Таким долгожительством может гордиться далеко не каждая микросхема и даже не каждый транзистор. Так что же такого особенного в этой микросхеме, имеющей в своей маркировке три пятерки?

Одной из легенд электроники является микросхема интегрального таймера NE555 . Разработана она была в далеком 1972 году. Таким долгожительством может гордиться далеко не каждая микросхема и даже не каждый транзистор. Так что же такого особенного в этой микросхеме, имеющей в своей маркировке три пятерки?

Серийный выпуск микросхемы NE555 начала компания Signetics ровно через год после того, как ее разработал Ганс Р. Камензинд . Самым удивительным в этой истории было то, что на тот момент времени Камензинд был практически безработным: он уволился из компании PR Mallory, но устроиться никуда не успел. По сути дела это была «домашняя заготовка».

Микросхема увидела свет и получила столь большую известность и популярность благодаря стараниям менеджера фирмы Signetics Арта Фьюри бывшего, конечно, приятелем Камензинда. Раньше он работал в фирме General Electric, поэтому знал рынок электроники, что там требуется, и чем можно привлечь внимание потенциального покупателя.

По воспоминаниям Камензинда А. Фьюри был настоящим энтузиастом и любителем своего дела. Дома у него была целая лаборатория, заполненная радиокомпонентами, где он и проводил различные исследования и опыты. Это давало возможность накапливать огромный практический опыт и углублять теоретические познания.

В то время продукция фирмы Signetics именовалась в виде «5**», и опытный, обладавший сверхъестественным чутьем в вопросах рынка электроники А. Фьюри, решил, что маркировка 555 (три пятерки) будет для новой микросхемы как нельзя кстати. И он не ошибся: микросхема пошла просто нарасхват, она стала, пожалуй, самой массовой за всю историю создания микросхем. Самое интересное, что свою актуальность микросхема не утратила и по сей день.

Несколько позднее в маркировке микросхемы появились две буквы, она стала называться NE555. Но поскольку в те времена в системе патентования существовала полная неразбериха, то интегральный таймер бросились выпускать все, кому не лень, естественно, поставив перед тремя пятерками другие (читай свои) буквы. Позднее на базе таймера 555 были разработаны сдвоенные (IN556N) и счетверенные (IN558N) таймеры, естественно, в более многовыводных корпусах. Но за основу был взят все тот же NE555.

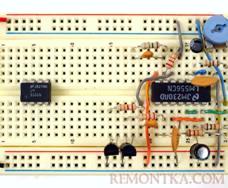

Рис. 1. Интегральный таймер NE555

555 в СССР

Первое описание 555 в отечественной радиотехнической литературе появилось уже в 1975 году в журнале «Электроника». Авторы статьи отмечали тот факт, что эта микросхема будет пользоваться не меньшей популярностью, чем широко известные уже в то время операционные усилители. И они нисколько не ошиблись. Микросхема позволяла создавать очень простые конструкции, причем, практически все они начинали работать сразу, без мучительной наладки. А ведь известно, что повторяемость конструкции в домашних условиях возрастает пропорционально квадрату ее «простоты».

В Советском Союзе в конце 80 – х годов был разработан полный аналог 555, получивший название КР1006ВИ1 . Первое промышленное применение отечественного аналога было в видеомагнитофоне «Электроника ВМ12».

Производители микросхемы NE555:

Внутреннее устройство микросхемы NE555

Прежде, чем схватиться за паяльник и начать сборку конструкции на интегральном таймере, давайте сначала разберемся, что там внутри и как все это работает. После этого понять, как работает конкретная практическая схема, будет намного проще.

Внутри интегрального таймера содержится свыше двадцати транзисторов , соединение которых показано на рисунке — https://remontka.com/wp-content/uploads/electro_all/555ic.jpg

Как видно, принципиальная схема достаточно сложна, и приведена здесь лишь для общей информации. Ведь все равно в нее паяльником не влезешь, отремонтировать ее не удастся. Собственно говоря, именно так выглядят изнутри и все другие микросхемы, как цифровые, так и аналоговые (см. — Легендарные аналоговые микросхемы ). Уж такова технология производства интегральных схем. Разобраться в логике работы устройства в целом по такой схеме тоже не удастся, поэтому ниже показана функциональная схема и приводится ее описание.

Технические данные

Но, перед тем как разбираться с логикой работы микросхемы, наверно, следует привести ее электрические параметры. Диапазон питающих напряжений достаточно широк 4,5…18В, а выходной ток может достигать 200мА, что позволяет использовать в качестве нагрузки даже маломощные реле. Сама же микросхема потребляет совсем немного: к току нагрузки добавляется всего 3…6мА. При этом точность собственно таймера от питающего напряжения практически не зависит, — всего 1 процент от расчетного значения. Дрейф составляет всего 0,1%/вольт. Также невелик и температурный дрейф – всего 0, 005%/°C. Как видно, все достаточно стабильно.

Функциональная схема NE555 (КР1006ВИ1)

Как было сказано выше, в СССР сделали аналог буржуйской NE555 и назвали его КР1006ВИ1. Аналог получился очень даже удачный, ничуть не хуже оригинала, поэтому использовать его можно, без всяких опасений и сомнений. На рисунке 3 показана функциональная схема интегрального таймера КР1006ВИ1. Она же полностью соответствует микросхеме NE555.

Рисунок 3. Функциональная схема интегрального таймера КР1006ВИ1

Сама микросхема не так уж и велика, — выпускается в восьмивыводном корпусе DIP8, а также в малогабаритном SOIC8. Последнее говорит о том, что 555 может использоваться для SMD – монтажа, другими словами интерес к ней у разработчиков сохранился до сих пор.

Внутри микросхемы элементов тоже немного. Основным является самый обычный RS – триггер DD1. При подаче логической единицы на вход R триггер сбрасывается в ноль, а при подаче логической единицы на вход S, естественно, устанавливается в единицу. Для формирования управляющих сигналов на RS – входах служит специальная схема на компараторах , о которой будет рассказано несколько позже.

Физические уровни логической единицы зависят, конечно, от используемого напряжения питания и практически составляют от Uпит/2 почти до полного Uпит. Примерно такое же соотношение наблюдается и у логических микросхем структуры КМОП. Логический же ноль находится, как обычно, в пределах 0…0,4В. Но эти уровни находятся внутри микросхемы, о них можно только догадываться, но руками их не пощупать, глазами не увидеть.

Выходной каскад

Для увеличения нагрузочной способности микросхемы, к выходу триггера подключен мощный выходной каскад на транзисторах VT1, VT2.

Если RS – триггер сброшен, то на выходе (вывод 3) присутствует напряжение логического нуля, т.е. открыт транзистор VT2. В случае, когда триггер установлен на выходе также уровень логической единицы.

Выходной каскад выполнен по двухтактной схеме, что позволяет подключать нагрузку между выходом и общим проводом (выводы 3,1) или шиной питания (выводы 3,8).

Небольшое замечание по выходному каскаду. При ремонте и наладке устройств на цифровых микросхемах одним из методов проверки схемы является подача на входы и выходы микросхем сигнала низкого уровня. Как правило, это делается замыканием на общий провод этих самых входов и выходов с помощью швейной иголки, при этом, не принося никакого вреда микросхемам.

В некоторых схемах питание NE555 составляет 5В, поэтому создается впечатление, что это тоже цифровая логика и с ней тоже можно обходиться достаточно вольно. Но на самом деле это не так. В случае с микросхемой 555, точнее с ее двухтактным выходом, такие «опыты» делать нельзя: если выходной транзистор VT1 в этот момент окажется в открытом состоянии, то получится короткое замыкание и транзистор просто сгорит. А уж если питающее напряжение будет близко к максимальному, то плачевный финал просто неизбежен.

Дополнительный транзистор (вывод 7)

Кроме упомянутых транзисторов имеется еще транзистор VT3. Коллектор этого транзистора соединен с выводом микросхемы 7 «Разрядка». Его назначение разряжать времязадающий конденсатор при использовании микросхемы в качестве генератора импульсов. Разряд конденсатора происходит в момент сброса триггера DD1. Если вспомнить описание триггера, то на инверсном выходе (обозначен на схеме кружком) в этот момент имеется логическая единица, приводящая к открыванию транзистора VT3.

О сигнале сброс (вывод 4)

Сбросить триггер можно в любой момент, — у сигнала «сброс» высокий приоритет. Для этого существует специальный вход R (вывод 4), обозначенный на рисунке как Uсбр. Как можно понять из рисунка сброс произойдет, если на 4 вывод подать импульс низкого уровня, не более 0,7В. При этом на выходе микросхемы (вывод 3) появится напряжение низкого уровня.

В тех случаях, когда этим входом не пользуются, на него подают уровень логической единицы, чтобы избавиться от импульсных помех. Проще всего это сделать, подключив вывод 4 напрямую к шине питания. Ни в коем случае нельзя оставлять его, что называется, в «воздухе». Потом долго придется удивляться и раздумывать, а почему же схема работает столь нестабильно?

Замечания о триггере «вообще»

Чтобы не запутаться совсем, в каком состоянии находится триггер, следует напомнить о том, что в рассуждениях о триггере всегда принимается во внимание состояние его прямого выхода. Уж, если сказано, что триггер «установлен», то на прямом выходе состояние логической единицы. Если говорят, что триггер «сброшен», — на прямом выходе непременно состояние логического нуля.

На инверсном выходе (отмечен маленьким кружком) все будет с точностью до наоборот, поэтому, часто выход триггера называют парафазным. Чтобы не перепутать все еще раз, об этом больше говорить не будем.

Тот, кто внимательно дочитал вот до этого места, может спросить: «Позвольте, ведь это же просто триггер с мощным транзисторным каскадом на выходе. А где же собственно сам таймер?» И будет прав, поскольку до таймера дело еще и не дошло. Чтобы получился таймер его отец – создатель Ганс Р. Камензинд изобрел оригинальный способ управления этим триггером. Вся хитрость этого способа заключается в формировании сигналов управления.

Формирование сигналов на RS – входах триггера

Итак, что же у нас получилось? Всем делом внутри таймера заправляет триггер DD1: если он установлен в единицу, — на выходе микросхемы напряжение высокого уровня, а если сброшен, то на выводе 3 низкий уровень и вдобавок открыт транзистор VT3. Назначение этого транзистора — разряд времязадающего конденсатора в схеме, например, генератора импульсов.

Управление триггером DD1 осуществляется с помощью компараторов DA1 и DA2. Для того, чтобы управлять работой триггера на выходах компараторов нужно получить сигналы R и S высокого уровня. На один из входов каждого компаратора подано опорное напряжение, которое формируется прецизионным делителем на резисторах R1…R3. Сопротивление резисторов одинаково, поэтому поданное на них напряжение делится на 3 равные части.

Формирование сигналов управления триггером

Запуск таймера

На прямой вход компаратора DA2 подано опорное напряжение величиной 1/3U, а внешнее напряжение запуска таймера Uзап через вывод 2 подано на инверсный вход компаратора. Для того, чтобы воздействовать на вход S триггера DD1 на выходе этого компаратора необходимо получить высокий уровень. Это возможно в том случае, если напряжение Uзап будет находиться в пределах 0…1/3U.

Даже кратковременный импульс такого напряжения вызовет срабатывание триггера DD1 и появление на выходе таймера напряжения высокого уровня. Если на вход Uзап воздействовать напряжением выше 1/3U и вплоть до напряжения питания, то никаких изменений на выходе микросхемы не произойдет.

Останов таймера

Для останова таймера надо просто сбросить внутренний триггер DD1, а для этого на выходе компаратора DA1 сформировать сигнал R высокого уровня. Компаратор DA1 включен несколько иначе, чем DA2. Опорное напряжение величиной 2/3U подано на инвертирующий вход, а управляющий сигнал «Порог срабатывания» Uпор подан на прямой вход.

При таком включении высокий уровень на выходе компаратора DA1 возникнет лишь тогда, когда напряжение Uпор на прямом входе превысит опорное напряжение 2/3U на инвертирующем. В этом случае произойдет сброс триггера DD1, а на выходе микросхемы (вывод 3) установится сигнал низкого уровня. Также произойдет открывание «разрядного» транзистора VT3, который и разрядит времязадающий конденсатор.

Если входное напряжение находится в пределах 1/3U…2/3U, не сработает ни один из компараторов, изменение состояния на выходе таймера не произойдет. В цифровой технике такое напряжение называется «серый уровень». Если просто соединить выводы 2 и 6, то получится компаратор с уровнями срабатывания 1/3U и 2/3U. И даже без единой дополнительной детали!

Изменение опорного напряжения

Вывод 5, обозначенный на рисунке как Uобр, предназначен для контроля опорного напряжения или его изменения с помощью дополнительных резисторов. Также на этот вход возможна подача управляющего напряжения, благодаря чему возможно получения частотно или фазо модулированного сигнала. Но чаще этот вывод не используется, а для уменьшения влияния помех соединяется с общим проводом через конденсатор небольшой емкости.

Питание микросхемы осуществляется через выводы 1 – GND, 2 +U.

Вот собственно описание интегрального таймера NE555. На таймере собрано множество всяких схем, которые будут рассмотрены в следующих статьях.

Продолжение статьи: Конструкции на интегральном таймере 555

Информация, опубликованная на данном веб-сайте, представлена исключительно в ознакомительных целях, за применение этой информации администрация сайта ответственности не несет.